کشف نقص جدیدی در پردازنده های اینتل با امکان انجام حملات Side-Channel

اخبار داغ فناوری اطلاعات و امنیت شبکه

تحقیقات جدید نشان میدهد که با بهره گیری از اولین side-channel "on-chip, cross core" در پردازنده های کافی لِیک و استارلِیک اینتل، به عنوان راه دیگری برای سرقت اطلاعات حساس میتوان استفاده کرد.

این یافته ها توسط گروهی از دانشگاهیان دانشگاه ایلینویز در اوربانا شمپین منتشر شده است و انتظار میرود که یافته ها در سمپوزیوم امنیتی USENIX که در ماه آگوست برگزار میگردد، ارائه شوند.

در حالی که قبلا تصور میشد که حملات نشت اطلاعات با هدف قرار دادن ریزطراحی پردازنده، باعث از بین بردن فضای ایزوله بین برنامه های کاربر و سیستم عامل می شود و به برنامه مخرب اجازه می دهد تا به حافظه مورد استفاده توسط برنامه های دیگر (به عنوان مثال Meltdown و Spectre) دسترسی پیدا کند؛ اما این حمله جدید از اختلاف موجود در اتصال حلقه ها استفاده میکند.

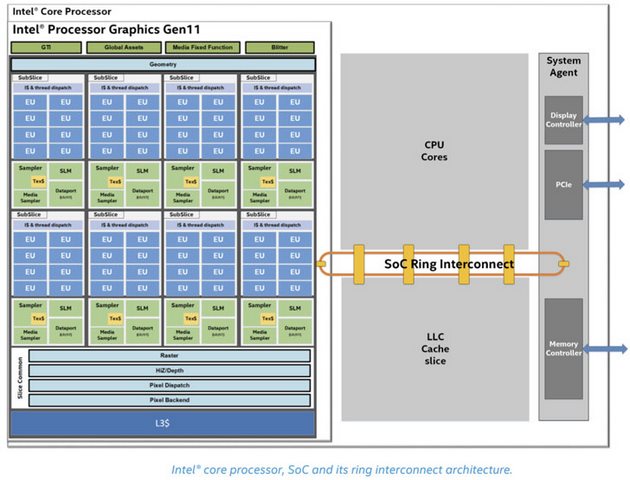

SoC Ring interconnect یک ساختار پیوسته و در حال حرکت است که در یک توپولوژی حلقه ای مرتب شده و امکان ایجاد ارتباط درون فرآیندی بین اجزای مختلف (با نام agents) مانند هسته ها ، سطح آخر حافظه پنهان (LLC) ، واحد گرافیک و عامل سیستم را که درون پردازنده قرار دارد، فراهم می کند. هر حلقه از طریق آنچه که ring stop نامیده می شود با حلقه دیگر ارتباط برقرار می کند.

برای نیل به این هدف، محققان پروتکل های اتصال حلقه ها را مهندسی معکوس کردند تا شرایط دو یا چند فرایند را برای ایجاد این اختلاف فراهم کنند و در جای خود، از آنها ایجاد یک کانال مخفی با ظرفیت 4.18 مگابیت بر ثانیه استفاده کردند ، که به گفته محققان بر خلاف Flush + Flush یا Flush + Reload ، تاکنون جز بزرگترین کانالهای cross-core غیر متکی به حافظه مشترک بوده است.

ریكاردو پاكاگنلا، یکی از نویسندگان این تحقیق افزود: "مهم این است كه برخلاف حملات قبلی ، حملات ما متکی بر به اشتراك گذاردن حافظه، حافظه پنهان، منابع core-private یا هر ساختار خاص دیگری نیست. "در نتیجه، با استفاده از تکنیک های موجود "ایزولاسیون دامنه"، تعدیل آنها دشوار است".

محققان با مشاهده اینکه توقف حلقه ای همیشه ترافیکی را که در حال حاضر در این حلقه است، نسبت به ترافیک جدیدی که از طرف عوامل آن وارد می شود، ترجیح می دهد، گفت: "هنگامی که ترافیک موجود در on-ring، ورود ترافیک حلقه جدید را به تأخیر بیاندازد، اختلاف ایجاد می شود".

با استفاده از این اطلاعات ، یک مهاجم می تواند تاخیر در دسترسی به حافظه مرتبط با یک فرایند مخرب را به دلیل اشباع ظرفیت پهنای باند ناشی از دسترسی های حافظه فرآیند قربانی، اندازه گیری نماید. با این حال، این امر مستلزم آن است که روند جاسوسی به طور مداوم در حافظه پنهان اختصاصی خود (L1-L2) از دست برود و اقدامات را از یک قطعه LLC هدف انجام دهد.

با این کار، تأخیر مکرر در بارگذاری های حافظه از LLC به دلیل تداخل حلقه می تواند به یک مهاجم اجازه دهد تا از اندازه گیری ها به عنوان یک کانال جانبی برای نشت key bit ها از EdDSA آسیب پذیر و پیاده سازی های RSA و همچنین بازسازی رمزهای عبور با محاسبه و استخراج زمان دقیق کلیدهای تایپ شده توسط کاربر قربانی، استفاده کند.

به طور خاص، "یك مهاجم با آگاهی از اقدامات و تلاش های مهندسی معكوس ما، می تواند این بارگذاری را به گونه ای تنظیم كند كه بارگذاری ها به شکل تضمین شده ای با بارگذاری های اولین فرآیند مقابله كند؛ متعاقبا با سوءاستفاده از برنامه ریزی حملات حافظه پنهان، برای جلوگیری از بارگذاری اطلاعات قربانی در حافظه پنهان، تداخل در حلقه را در حالی که قربانی در حال محاسبه است مانیتور کرده و یک machine learning classifier استاندارد را برای ردیابی نویزها و بیت های نشت به کار می برد".

این مطالعه همچنین نشان میدهد اولین باری که یک کانال ریز معماری مبتنی بر تداخل برای حملات زمان سنج کلید مورد سو استفاده کاربر قرار می گیرد تا داده حساس تایپ شده توسط قربانی را تجزیه و تحلیل کند، را چه زمانی بوده است.

در پاسخ به افشای اطلاعات، اینتل این حملات را به عنوان "Traditional side channel" دسته بندی میکند. این حملات به کلاس حملات اوراکل اشاره میکند که به طور معمول از اختلاف در زمان اجرا برای تجزیه و تحلیل بهره میبرند، استفاده میکنند.

راهنمایی های سازنده تراشه برای مقابله با حملات زمان بندی شده در برابر پیاده سازی رمزنگاری شده، رعایت اصول برنامه نویسی زمان ثابت را توصیه مینماید. لازم به ذکر است:

زمان اجرا مستقل از مقادیر مخفی است.

ترتیب اجرای دستورالعمل ها (با نام code access patterns) مستقل از مقادیر مخفی هستند.

ترتیب بارگذاری و ذخیره عملگرهای حافظه (data access pattern) مستقل از مقادیر مخفی هستند.

برچسب ها: اوراکل, حافظه پنهان, پردازنده, اینتل, Oracle, RSA, EdDSA, Cache, Domain isolation, Ring Stop, SoC Ring interconnect, USENIX, Skylake, Coffee Lake, Side-channel, LLC, CPU, Intel